- 您现在的位置:买卖IC网 > Sheet目录3872 > PIC18F2321T-I/ML (Microchip Technology)IC PIC MCU FLASH 4KX16 28QFN

PIC18F2221/2321/4221/4321 FAMILY

DS39689F-page 108

2009 Microchip Technology Inc.

10.5

RCON Register

The RCON register contains flag bits which are used to

determine the cause of the last Reset or wake-up from

Idle or Sleep modes. RCON also contains the IPEN bit

which enables interrupt priorities.

The operation of the SBOREN bit and the Reset flag

bits is discussed in more detail in Section 5.1 “RCON

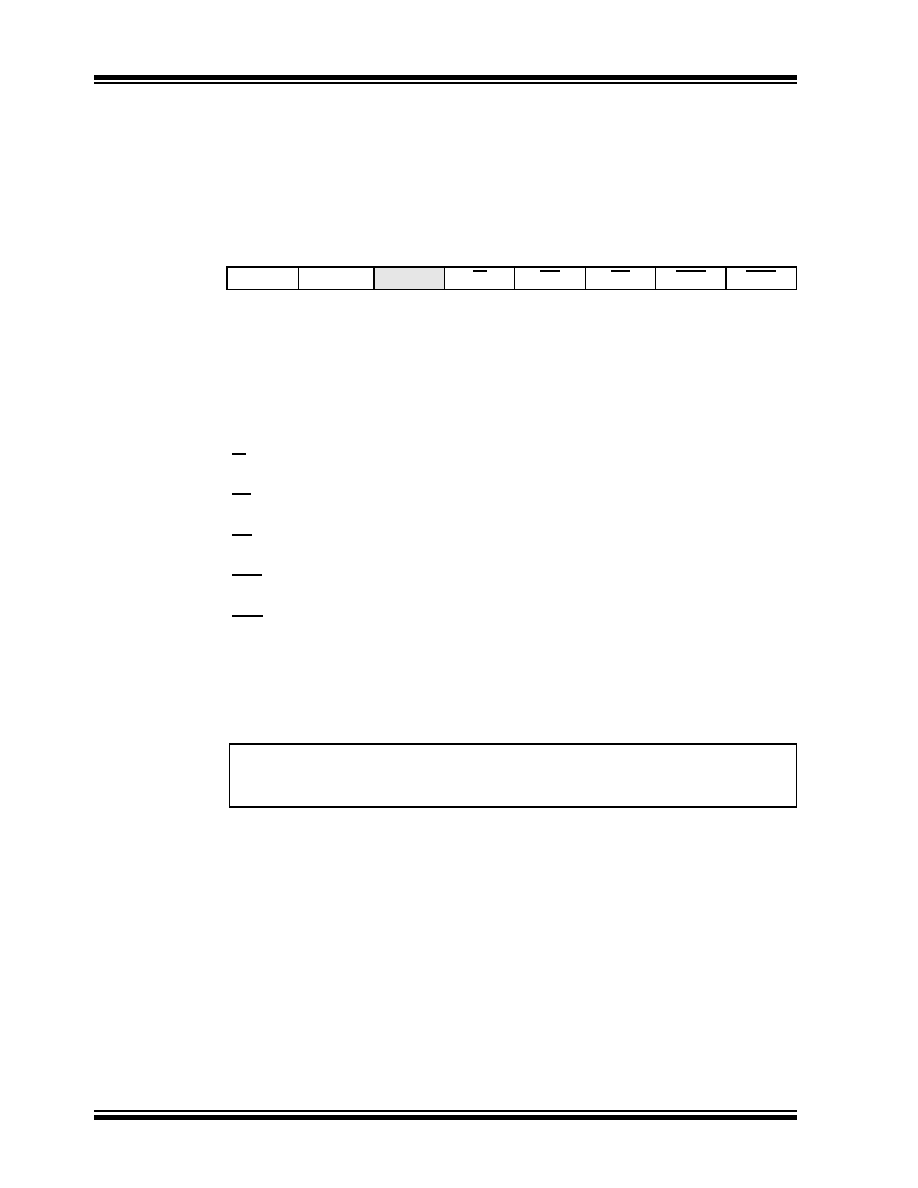

REGISTER 10-10: RCON: RESET CONTROL REGISTER

R/W-0

R/W-1(1)

U-0

R/W-1

R-1

R/W-0(2)

R/W-0

IPEN

SBOREN

—RI

TO

PD

POR

BOR

bit 7

bit 0

bit 7

IPEN: Interrupt Priority Enable bit

1 = Enable priority levels on interrupts

0 = Disable priority levels on interrupts (PIC16XXX Compatibility mode)

bit 6

SBOREN: Software BOR Enable bit(1)

For details of bit operation, see Register 5-1.

bit 5

Unimplemented: Read as ‘0’

bit 4

RI: RESET Instruction Flag bit

For details of bit operation, see Register 5-1.

bit 3

TO: Watchdog Time-out Flag bit

For details of bit operation, see Register 5-1.

bit 2

PD: Power-down Detection Flag bit

For details of bit operation, see Register 5-1.

bit 1

POR: Power-on Reset Status bit(2)

For details of bit operation, see Register 5-1.

bit 0

BOR: Brown-out Reset Status bit

For details of bit operation, see Register 5-1.

Note 1: If SBOREN is enabled, its Reset state is ‘1’; otherwise, it is ‘0’.

2: Actual Reset values are determined by device configuration and the nature of the

device Reset. See Register 5-1 for additional information.

Legend:

R = Readable bit

W = Writable bit

U = Unimplemented bit, read as ‘0’

-n = Value at POR

‘1’ = Bit is set

‘0’ = Bit is cleared

x = Bit is unknown

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

PIC18F2221T-I/SO

IC PIC MCU FLASH 2KX16 28SOIC

PIC16LF1939-I/MV

IC MCU 8BIT 28KB FLASH 40-UQFN

PIC24F16KL402-I/SP

IC MCU 16BIT 16KB FLASH 28-SPDIP

PIC18F24J11-I/SS

IC PIC MCU FLASH 16K 2V 28-SSOP

PIC24F16KA101-I/SO

IC PIC MCU FLASH 16K 20-SOIC

PIC16C57C-04/P

IC MCU OTP 2KX12 28DIP

PIC16CE623-04/SO

IC MCU OTP 512X14 EE COMP 18SOIC

PIC16C57C-04/SP

IC MCU OTP 2KX12 28DIP

相关代理商/技术参数

PIC18F2321T-I/SO

功能描述:8位微控制器 -MCU 8 KB Flash 512 RAM RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18F2321T-I/SS

功能描述:8位微控制器 -MCU 8KB Flash 512bytes RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18F2331-E/ML

功能描述:8位微控制器 -MCU 8KB 768 RAM 22 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18F2331-E/MM

功能描述:8位微控制器 -MCU 8KB 768 RAM 22 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18F2331-E/SO

功能描述:8位微控制器 -MCU 8KB 768 RAM 22 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18F2331-E/SP

功能描述:8位微控制器 -MCU 8KB 768 RAM 22 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18F2331-I/ML

功能描述:8位微控制器 -MCU 8KB 768 RAM 22 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18F2331-I/MM

功能描述:8位微控制器 -MCU 8KB 768 RAM 22 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT